## (12) United States Patent

Dixon et al.

### (54) APPARATUS AND METHOD FOR MEMORY WITH BIT SWAPPING ON THE FLY AND **TESTING**

(75) Inventors: **R. Paul Dixon**, Carrollton, TX (US); David R. Resnick, Eau Claire, WI (US); Gerald A. Schwoerer, Chippewa Falls, WI (US); Kelly J. Marquardt, Eau Claire, WI (US); Alan M. Grossmeier, Chippewa Falls, WI (US); Michael L. Steinberger, Chippewa Falls, WI (US); Van L. Snyder, Eau Claire, WI (US); Roger A. Bethard, Chippewa Falls, WI (US); Michael F. Higgins, Eau Claire, WI (US)

Assignee: Cray Inc., Seattle, WA (US)

Subject to any disclaimer, the term of this (\*) Notice: patent is extended or adjusted under 35

U.S.C. 154(b) by 494 days.

Appl. No.: 10/850,057 (21)

(22)Filed: May 19, 2004

#### (65)**Prior Publication Data**

US 2005/0022065 A1 Jan. 27, 2005

### Related U.S. Application Data

- (60) Provisional application No. 60/472,174, filed on May 20, 2003.

- (51) Int. Cl. H03M 13/00 (2006.01)

- (52) **U.S. Cl.** ...... **714/758**; 714/718; 714/733

- Field of Classification Search ....... 714/718–723, 714/754, 7, 752, 823, 742, 819, 799 See application file for complete search history.

#### US 7,320,100 B2 (10) **Patent No.:**

(45) Date of Patent: Jan. 15, 2008

#### (56)References Cited

#### U.S. PATENT DOCUMENTS

4,319,357 A 3/1982 Bossen 4,384,348 A \* 5/1983 Nozaki ...... 365/201 4,394,763 A 7/1983 Nagano et al. 4,667,330 A 5/1987 Kumagai 4,757,503 A 7/1988 Hayes et al. 4,782,486 A 11/1988 Lipcon et al.

(Continued)

#### FOREIGN PATENT DOCUMENTS

EP 0441088 8/1991

(Continued)

Primary Examiner—Guy Lamarre Assistant Examiner—Sam Rizk

(74) Attorney, Agent, or Firm-Charles A. Lemaire; Lemaire Patent Law Firm, P.L.L.C.

#### **ABSTRACT**

A memory controller and method that provide a read-refresh (also called "distributed-refresh") mode of operation, in which every row of memory is read within the refresh-rate requirements of the memory parts, with data from different columns within the rows being read on subsequent readrefresh cycles until all rows for each and every column address have been read, scrubbing errors if found, thus providing a scrubbing function that is integrated into the read-refresh operation, rather than being an independent operation. For scrubbing, an atomic read-correct-write operation is scheduled. A variable-priority, variable-timing refresh interval is described. An integrated card self-tester and/or card reciprocal-tester is described. A memory bitswapping-within-address-range circuit, and a method and apparatus for bit swapping on the fly and testing are described.

#### 45 Claims, 15 Drawing Sheets

# US 7,320,100 B2 Page 2

| U.S. PATENT                           | DOCUMENTS               | 6,434,648                |         |         | Assour et al.          |

|---------------------------------------|-------------------------|--------------------------|---------|---------|------------------------|

| 4.000.553.4. 10/1000                  |                         | 6,463,001                |         | 10/2002 | Williams 365/222       |

| , , , , , , , , , , , , , , , , , , , | Arlington et al.        | 6,658,610                | B1 * 1  | 12/2003 | Chai et al 714/718     |

| , ,                                   | Chau et al.             | 6,779,128                | B1 *    | 8/2004  | Gale et al 714/6       |

| 5,267,242 A 11/1993                   | Lavallee et al.         | 6,796,501                | B2      | 9/2004  | Omet                   |

| 5,274,648 A * 12/1993                 | Eikill et al 714/719    | 6,879,530                | B2 *    | 4/2005  | Callaway et al 365/201 |

| / /                                   | Matsumoto et al 714/710 | 6,898,101                | B1      | 5/2005  | Mann                   |

| 5,357,621 A 10/1994                   |                         | 6,901,541                | B2      | 5/2005  | Antosh et al.          |

| 5,400,342 A 3/1995                    | Matsumura et al.        | 6,944,694                | B2 *    | 9/2005  | Pax 710/107            |

| 5,406,565 A 4/1995                    | MacDonald               | 7,073,112                | B2 *    | 7/2006  | Chai et al 714/733     |

| 5,430,859 A 7/1995                    | Norman et al.           | 7.088.713                |         |         | Battle et al 370/389   |

| 5,495,491 A * 2/1996                  | Snowden et al 714/764   | 2002/0116668             |         |         | Chhor et al.           |

| 5,502,814 A 3/1996                    | Yuuki et al.            | 2005/0053057             | A1*     | 3/2005  | Deneroff et al 370/360 |

| 5,533,194 A 7/1996                    | Albin et al.            | 2007/0067556             | A1*     | 3/2007  | Dixon et al 711/106    |

| 5,745,508 A 4/1998                    | Prohofsky               |                          |         |         |                        |

| 5,751,728 A 5/1998                    | Katanosaka              | FOREIGN PATENT DOCUMENTS |         |         |                        |

| 5,774,646 A * 6/1998                  | Pezzini et al 714/42    |                          | · ·     |         | TI BOCOMENTO           |

| 5,787,101 A 7/1998                    | Kelly                   | EP                       | 0 849 7 | 43 A3   | 8/1999                 |

| 6,226,766 B1* 5/2001                  | Harward 714/719         | JP 20                    | 030159  | 066     | 1/2003                 |

| 6,229,727 B1* 5/2001                  | Doyle 365/63            |                          |         |         |                        |

| / /                                   | Hunter                  | * cited by examiner      |         |         |                        |

FIG. 1B

FIG.2A

FIG.2D

Jan. 15, 2008

FIG.6

# APPARATUS AND METHOD FOR MEMORY WITH BIT SWAPPING ON THE FLY AND TESTING

#### RELATED APPLICATIONS

Benefit is claimed under 35 U.S.C. 119(e) to U.S. Provisional Application Ser. No. 60/472,174, entitled "APPARATUS AND METHOD FOR TESTING MEMORY CARDS" by David R. Resnick et al., filed May 20, 2003, which is 10 herein incorporated in its entirety by reference.

This application is also related to U.S. application Ser. No. 10/850,044, titled "APPARATUS AND METHOD FOR TESTING MEMORY CARDS" filed on even date herewith, which is incorporated herein by reference.

#### FIELD OF THE INVENTION

This invention relates to the field of computer memories, and more specifically to a method and apparatus for enhanc- 20 ing performance, reliability and availability in a computer memory by providing, in each word in memory, one or more spare bits and a circuit that can switch the spare bits in specified sections of memory dynamically (in real time) while the system is running and using data from the section 25 being switched, and to circuitry that allows functions of the card to be tested from the same card or from another memory card that is connected through a test apparatus. The apparatus and method allow selecting from among a plurality of ways to perform memory refresh in DRAM memories 30 according to which way is more efficient, providing variable timing for each cycle of refresh, and performing memory scrubbing which removes transient errors from the memory being controlled. An atomic read-correct-write can be scheduled to go back and fix a memory location after an error is 35 detected in data, where the data was earlier corrected and sent to a processor.

#### BACKGROUND OF THE INVENTION

Controllers for DRAMs (dynamic random-access memories) have been getting more complex over time as the data rates to memory have been increasing, but also as the features built into the memory parts have become more elaborate. For example, having multiple memory banks in 45 the memory parts (chips) adds significantly to the design complexity of a controller that attempts to use the capability of such memory parts to better advantage.

Over time and as a result of multiple causes, computer memories will have data errors. Only purchasers of inexpensive PCs tolerate the inconvenience of memories that do not have ECC (error-correction code) circuitry. One common ECC type is an SECDED (single-error correct, double-error detect) ECC. There are numerous different well-known codes that can be used to achieve such a function.

As the density of memory chips keeps increasing, the individual memory bits become more sensitive to upset and therefore to data loss. Data failures that do not result in (or result from) permanent IC failures, such that the memory part still functions correctly, are called soft errors. These soft 60 errors can be caused by familiar mechanisms like alpha particles but also, increasingly, by other mechanisms like other heavy ions and power-supply noise. The sensitivity to data loss increases geometrically as process rules shrink and power-supply voltages are reduced, while the total number 65 of bits per processor also increases geometrically because of user memory-size requirements. This means that soft-error

2

rates for systems coming on line will increase by orders of magnitude over historic error-rate norms.

In the past, soft memory errors have generally been handled by error-correction codes: SECDED and the like. Other correction technologies exist, and are sometimes used, but become increasingly expensive as a fraction of total memory cost as the correction and recovery capability is improved. For example, U.S. Pat. No. 5,745,508 "ERROR-DETECTION CODE" by Thomas Prohofsky, which is incorporated herein by reference, discusses SECDED codes that also detect certain three-bit and four-bit errors; and U.S. Pat. No. 4,319,357 "DOUBLE ERROR CORRECTION USING SINGLE ERROR CORRECTING CODE" by Bossen, which is incorporated herein by reference, discusses correcting certain hard-soft double-error combinations.

U.S. patent application Ser. No. 09/407,428 filed Sep. 29, 1999 and entitled "MULTIPROCESSOR NODE CONTROLLER CIRCUIT AND METHOD" by Deneroff et al. describes a system that can use ECC memory.

All DRAM parts need to be refreshed; that is what the D (dynamic) in the DRAM name indicates: one must cycle the memory repeatedly in order that the dynamic contents (the stored charges) of the capacitive store of each memory bit are regenerated. This "refresh" function is typically managed by having the memory parts themselves perform the refresh operation. This function generally takes place after a specific command is sent from the local memory controller using a specific request rate so that all memory bits are referenced within the required refresh interval.

Some features that have been in some controllers in the past and whose recognized benefits indicate that they are likely to be used in new designs are memory refresh, memory scrubbing, and support for spare bits in memory. Conventional uses for a spare bit include the ability to logically rewire a card that has a stuck bit (a bit that is always zero or one) or a frequently failing signal on a pin of a memory part such that the card can be returned to correct operation without physical access to the failing pin, chip, or card. In the past, such rewiring typically required removing the card from the system. Logic circuits that provide rudimentary versions of these features with the card in place in a system have shortcomings, such as having to stop accesses from the processor, at least as regards a section of memory having a failed bit and perhaps entirely, in order to reconfigure the memory card to have the spare bit to replace the failed bit.

Electrical issues and pin limitations push memory system design in directions that put the memory controller(s) on the memory cards and also push the card interface to have higher data rates per pin in order to reduce the number of pins while keeping the card bandwidth in line with the higher performance needs of the attached processors and of 55 the bandwidth of the memory components on the memory cards. A memory card design that adopts this direction has test issues, in that the memory components (the chips) are not directly accessible for testing as is normal in past industry practice, and the data rates of the high-speed interfaces are too fast for connection to testers that are available in normal production testing. While special purpose test equipment can be built and used, the design of special-purpose memory testers is very expensive and time consuming.

Thus, there is a need for improved methods and circuits in memory subsystems and for logic functions in which memory performance, reliability (the time between system

failures, or the inverse of failure frequency) and availability (the percentage of time the system is up and working) are improved.

#### SUMMARY OF THE INVENTION

Some embodiments of the invention provide a memory daughter card (MDC) for a computer system that uses one or more MDCs, wherein each MDC includes, in some embodiments, a W-circuit and a plurality of memory parts or chips. 10 The W-circuit provides a large variety of complex functions that support and enhance the function of the MDC, such as test, refresh, bit-swap, high-speed serial interface, command and access buffering, error-correction-code generation, checking and corrections, address-range checking, and/or 15 command interleaving functions etc.

In some embodiments, each memory controller can swap a spare bit into operation in a section of memory, dynamically in the background (i.e., in some embodiments, the swap is performed as part of the regular read-refresh opera- 20 tions, performed in the background during and while normal processor operations proceed in the foreground), while keeping the data in its normally addressed locations and even allowing functional processing to continue to the affected memory locations during the swap operation. One 25 at a time, each word in the affected portion of memory is read using the normal bit mapping, corrected if necessary, and then written to the same address but using the bitswapped mapping. Some embodiments use pointers that define the start address and end address of the bit-swapped 30 portion of memory, such that regular processor read operations and write operations use the bit-swapped mapping for the portion that has been swapped, and use the normal bit mapping for the portion that has not been swapped. This allows the bit swapping operations and regular processor 35 read operations and write operations to be performed at the same time (though individual operations are interleaved).

Some embodiments also allow spare-bit positions to be moved; for example a memory configured with bit-3, say, as the position of the spare could be reconfigured so that bit-11 (or any other bit in the data path) becomes the spare-bit, all while system operation is ongoing. Thus, the spare bit or bits can be configured to start out in any bit position or bit positions in the memory data path, and can be moved to any other position(s) during system operation.

Another aspect of the invention, in some embodiments, includes a bit-shifting circuit that allows bit replacement. i.e., allows any data bit, SECDED ECC bit, or other data-bit position to be disconnected or ignored, and effectively replaced using a spare bit. In some embodiments, an 50 address-range detection circuit is coupled to the bit-shifting circuit, wherein one or both of the address endpoints of the range are changed as the data is read out of the old bit positions, corrected if necessary, and then written back into the new bit positions. Normal read and write operations also 55 use the address-range detection circuit such that operations within the bit-replaced address range use the bit-shifted configuration, and operations not within the bit-replaced address range use the normal bit configuration. The present invention provides a memory daughter card (MDC) having 60 one or more (likely multiple) very high-speed serial interface(s), optionally an on-card L3 cache, and an on-card MDC test engine (or equivalently, a W-circuit test engine) that allows one MDC to be directly connected to another MDC, or to itself, for testing purposes. In some embodiments, a control interface, such as a JTAG interface and/or an IEEE-1394-type channel, allows the test engine to be

4

programmed and controlled by a test controller on a test fixture that allows a single card to be tested, or simultaneous testing of one or more pairs of MDCs, one MDC in a pair (the "golden" MDC) testing the other MDC of that pair.

Some embodiments of the invention provide a memory daughter card having a memory controller that provides a read-refresh (also called "distributed-refresh") mode of operation, in which every row of memory is read within the refresh-rate requirements of the memory parts, with data from different columns within the rows being read on subsequent read-refresh cycles until all rows for each and every column address have been read, at which point the process begins anew, thus reading every location in memory at a regular interval. While some previous controller implementations provided a refresh function using read commands (i.e., sending both row addresses and column addresses to access and cycle through all the memory rows,), the column address was a "don't care" value, thus ignoring which memory column is was selected in order to simplify their refresh function. In contrast, some embodiments of the present invention cycle through all the row addresses at a rate sufficient to refresh the memory parts at a given column (and actually reading the data and checking it), but these embodiments of the present invention also cycle through all the column addresses for the refresh commands, check the ECC for each word of data read, and correct any errors that are found, thus providing a scrubbing function that is integrated into the read-refresh operation, rather than being an independent operation. This satisfies the refresh-rate requirement to read every row within the specified rowrefresh interval, and also changes columns on each successive row-refresh interval, which is not required to provide the refresh function, but is provided in order to read and check the ECC on every location during this type of refresh.

In some embodiments, a scrubbing function is also provided (based on the checked ECC data) and is integrated into the read-refresh operation rather than being an independent operation. For scrubbing, in some embodiments, a subsequent atomic read-correct-write operation is scheduled based on each correctable single-bit error detected during the read-refresh operations (the separate read is done just in case the processor had modified the contents after the error was detected but before corrected data could have been written back, thus the read data from the request from which the error was detected, is not used for the write back of corrected data, but instead a new read is done as part of an atomic instruction) to correct the affected location. If no error was detected, then no scrubbing is needed. Other embodiments can selectively halt subsequent references to the memory bank whose data word is being scrubbed until the corrected data is returned to the memory part or it is determined that there was no error so that no write operation need take place.

In some embodiments, if a single-bit error is detected in a normal read operation from the processor, the error is fixed in the memory card and the corrected data are sent to the processor, and a supplemental atomic read-correct-write sequence is scheduled (as above, just in case the original processor or another processor had quickly modified the contents after the error was detected).

In some embodiments, a scrubbing function is provided in addition to an explicit-refresh (also called AutoRefresh) (i.e., scrubbing is interleaved with), such that all row addresses and all column addresses within each row are periodically read (e.g., about once per hour, in some embodiments, but in addition to and interspersed with the AutoRefresh, rather than instead of the AutoRefresh), and a correc-

tion sent if an error is detected. That is, is these embodiments, AutoRefresh is left on all the time, with the scrubbing function also running but in the background, for those cases where AutoRefresh uses less memory bandwidth than distributed refresh. In other embodiments, AutoRefresh mode of operation is alternatively selected instead of the read-refresh mode of operation to improve performance. That is, in some of these embodiments, AutoRefresh is run for about an hour, the read-refresh is run instead to scrub memory once and perform refresh while scrubbing, and then 10 AutoRefresh is again turned on.

In some embodiments, if using the read-refresh (distributed-refresh) mode of operation so that scrubbing and/or the spare-bit capability are all used as needed within the refresh function, the refresh rate (and therefore the rate of the 15 scrubbing and spare-bit functions) is set by the refresh requirements of the memory being controlled. In some embodiments, when the AutoRefresh function is instead being used for refresh, then the refresh frequency becomes fixed (e.g., a refresh request every 7.8 microseconds for 20 certain parts including certain DDR2 (Double Data Rate 2, a JEDEC memory standard for DRAM memory parts)), and the rates at which scrubbing and spare-bit insertion are done are set separately and independently from the refresh rate, generally at a much slower rate. In some embodiments, 25 when doing AutoRefresh and scrubbing only, the scrub rate is set slow (e.g., at a rate to scrub memory once every few hours); and if doing AutoRefresh, scrubbing and spare-bit insertion, the read-refresh (distributed-refresh) rate would be set to be fairly fast (in some embodiments, e.g., up to a rate 30 that would take about 10% or less of the memory band-

Some embodiments further provide one or more veryhigh-speed serial interfaces to the processor, and optionally an on-card L3 cache.

A method is also described, wherein one MDC executes a series of reads and writes (and optionally other commands) to another MDC to test at least some of the (and ideally, most or all of) other card's functions. A method is also described, wherein one port of an MDC executes a series of reads and 40 writes (and optionally other commands) to another port of the same MDC to test at least some of the (and ideally, most or all of) the card's functions.

It is to be understood that a memory "card" or "daughtercard" includes any suitable packaging, including printed 45 circuit card, ceramic module, or any other packaging that holds a plurality of memory chips along with some or all of the circuitry described herein. In some embodiments, a "card" would include a single integrated-circuit chip having both the memory and some or all of the circuitry described 50 herein

## BRIEF DESCRIPTION OF THE DRAWINGS

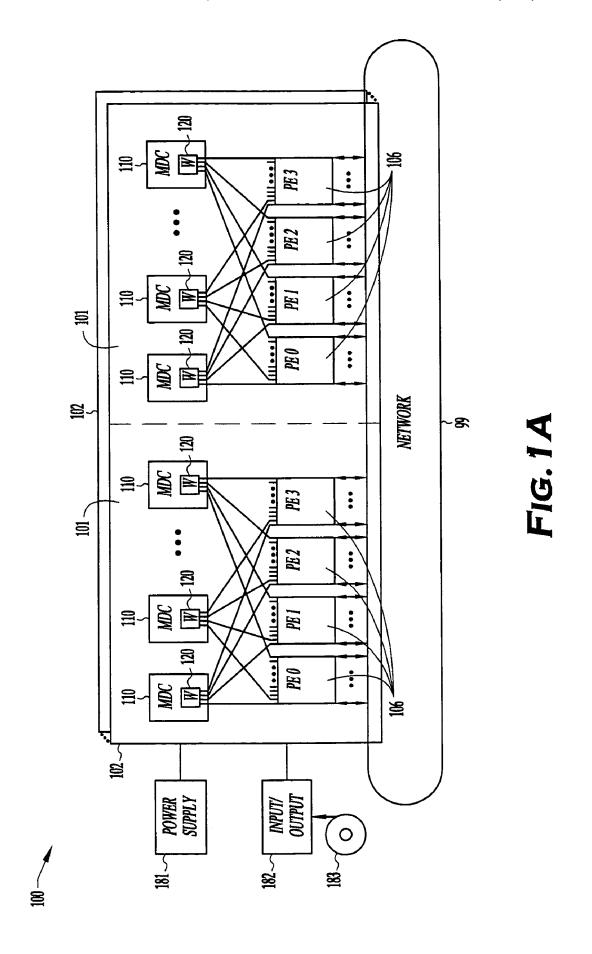

FIG. 1A is a block diagram of a computer system 100 of  $_{55}$  some embodiments of the invention.

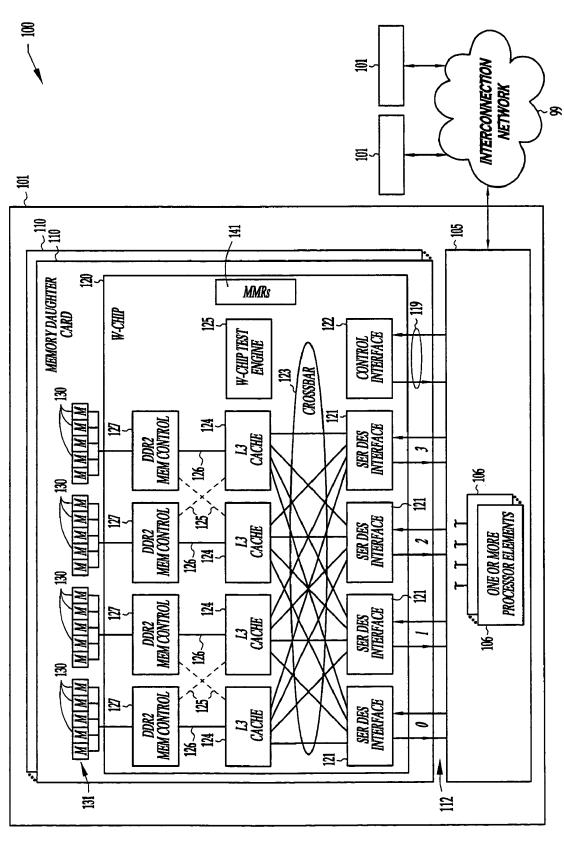

FIG. 1B is a block diagram of a different view of computer system 100 of some embodiments of the invention

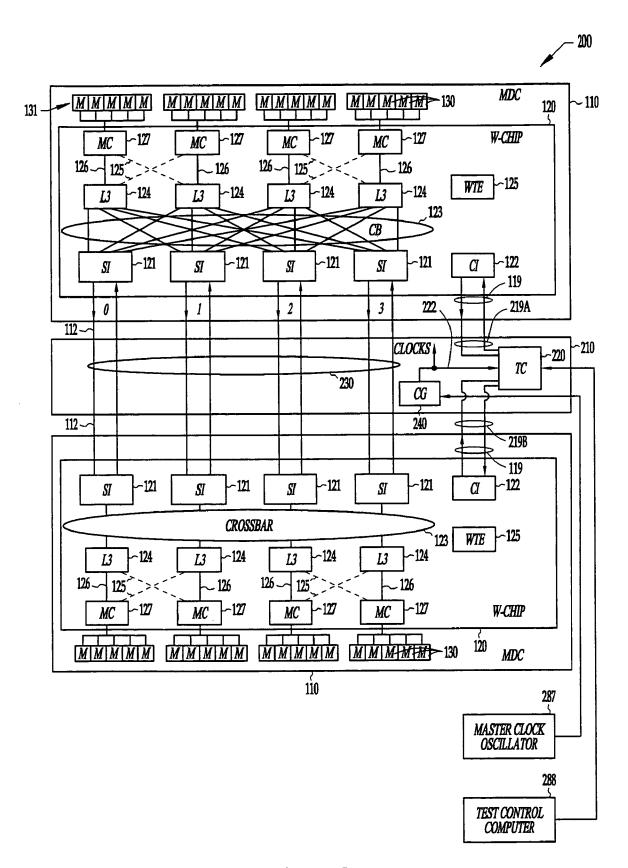

FIG. 2A is a block diagram of a memory-card testing 60 system 200 of some embodiments of the invention.

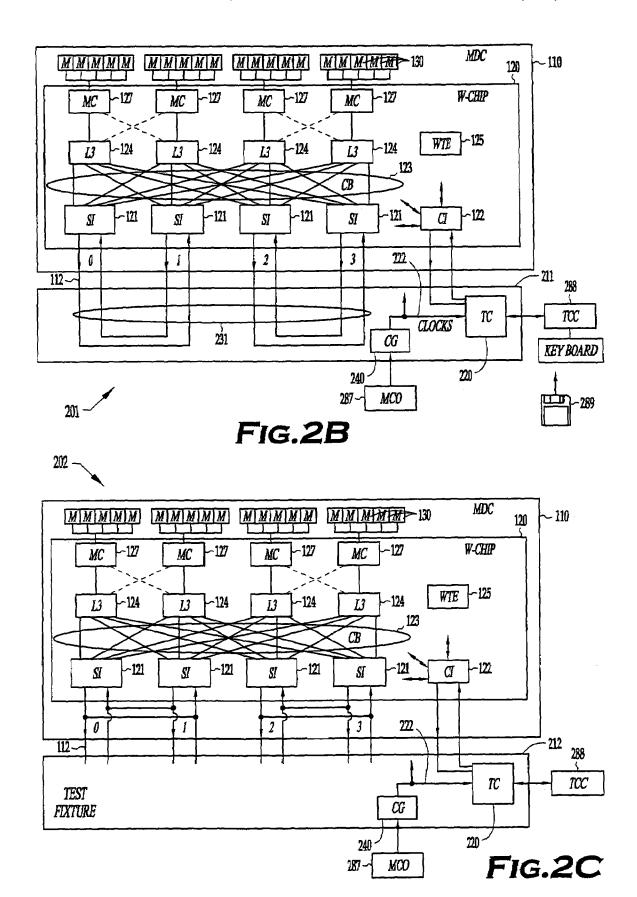

FIG. 2B is a block diagram of a memory-card testing system 201 of some embodiments of the invention.

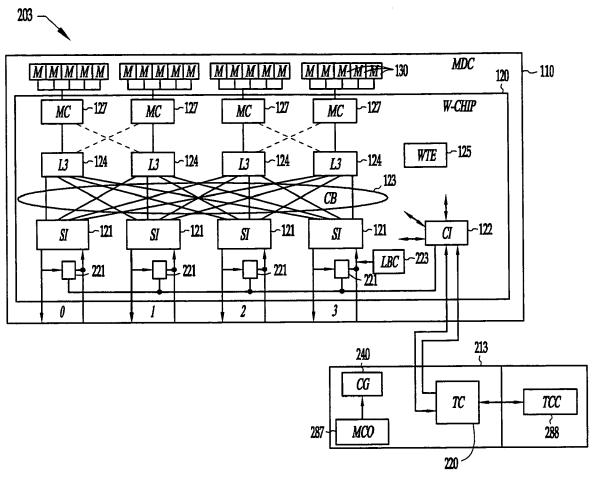

FIG. 2C is a block diagram of a memory-card testing system 202 of some embodiments of the invention.

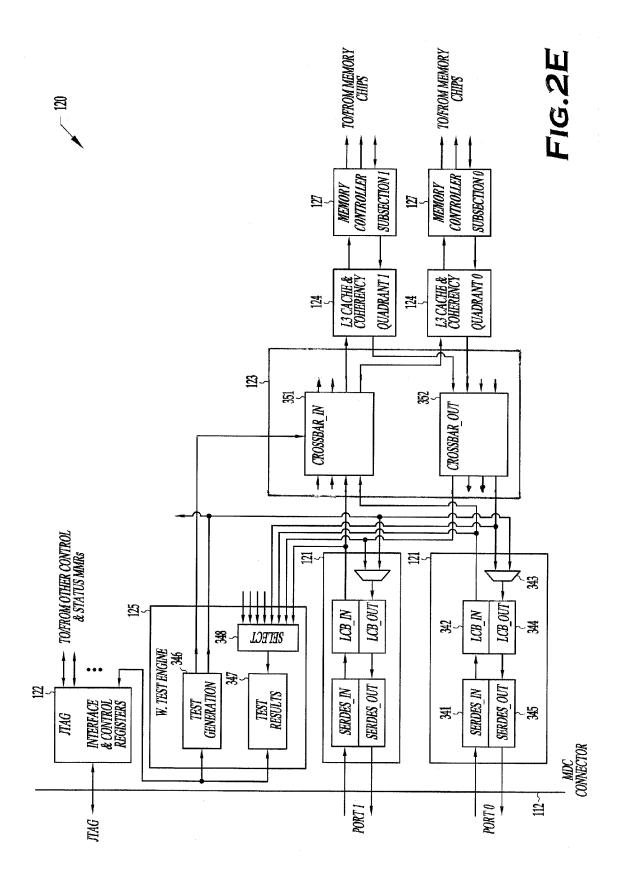

FIG. 2D is a block diagram of a memory-card testing system 203 of some embodiments of the invention.

6

FIG. 2E is a block diagram of a portion of W-circuit 120 of some embodiments of the invention.

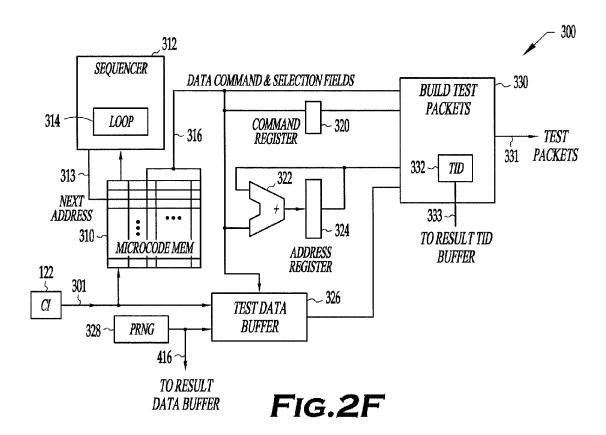

FIG. 2F is a block diagram of a test-engine processor 346 of some embodiments of the invention.

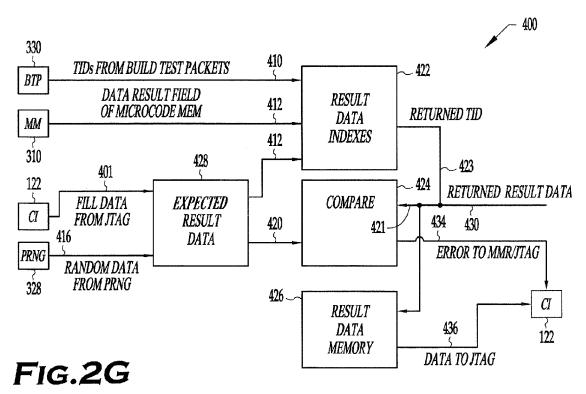

FIG. 2G is a block diagram of a test-engine test-result checker 347 of some embodiments of the invention.

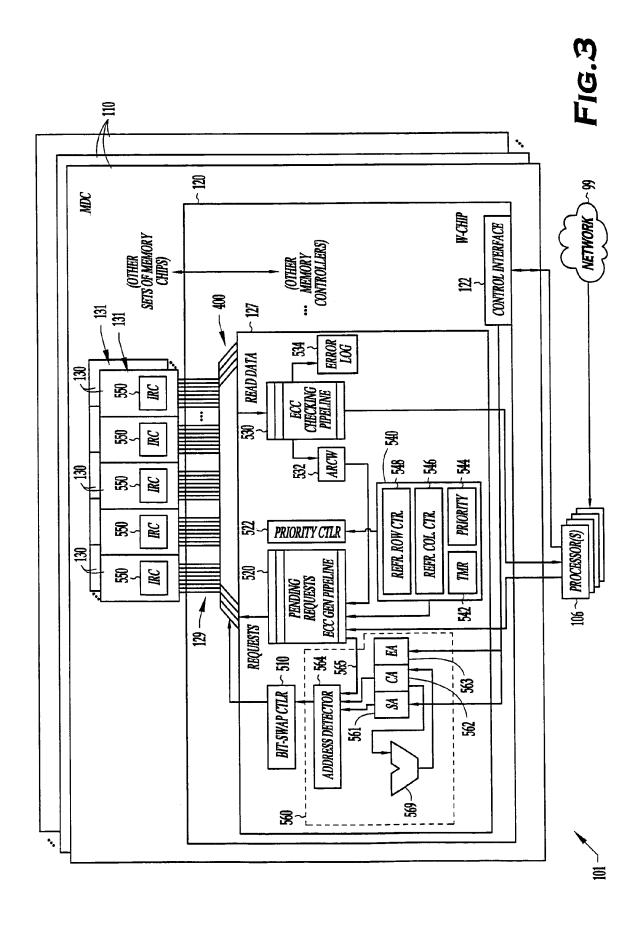

FIG. 3 is a block diagram of a computer system (node) 101 of some embodiments of the invention.

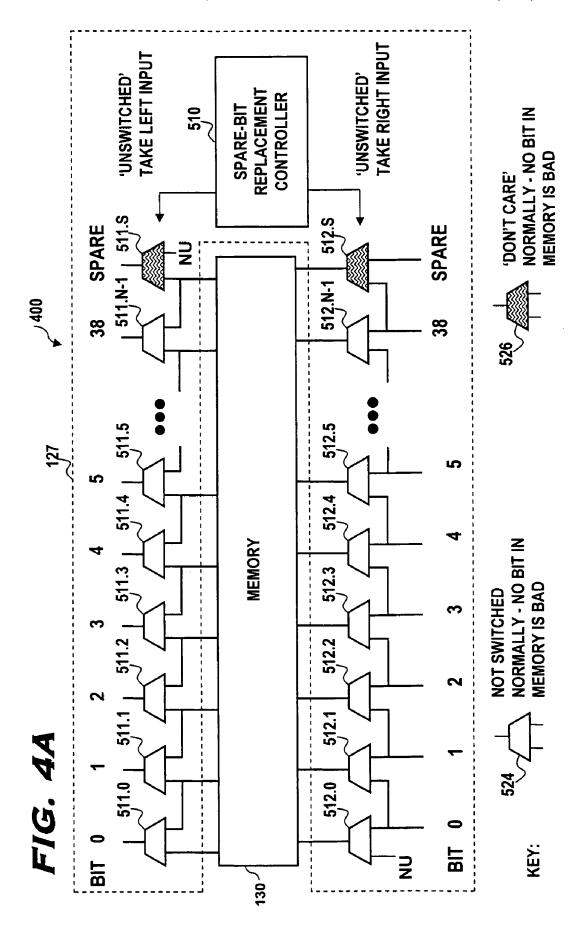

FIG. 4A is a block diagram of a non-activated bitswapping circuit 400 of some embodiments of the invention.

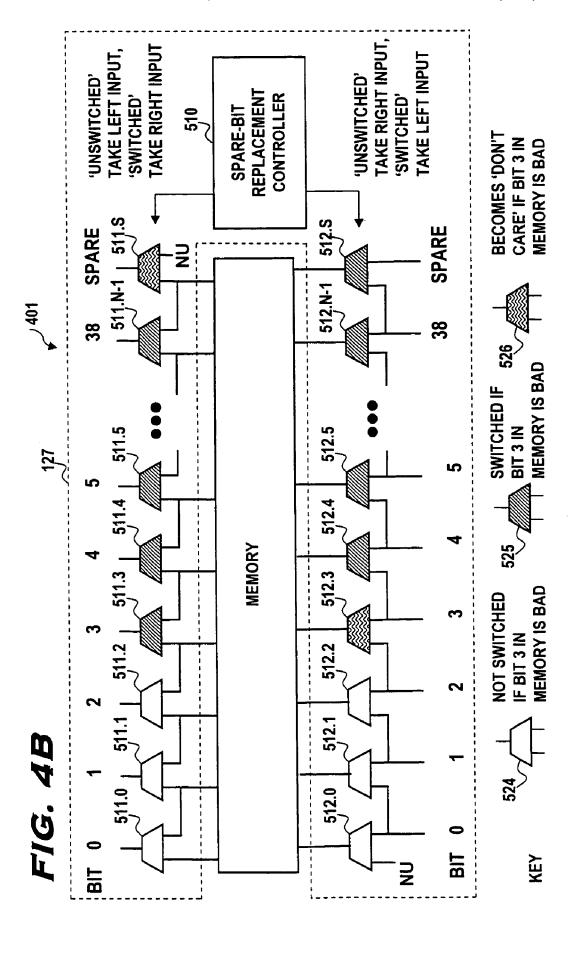

FIG. 4B is a block diagram of an activated bit-swapping circuit 401 of some embodiments of the invention.

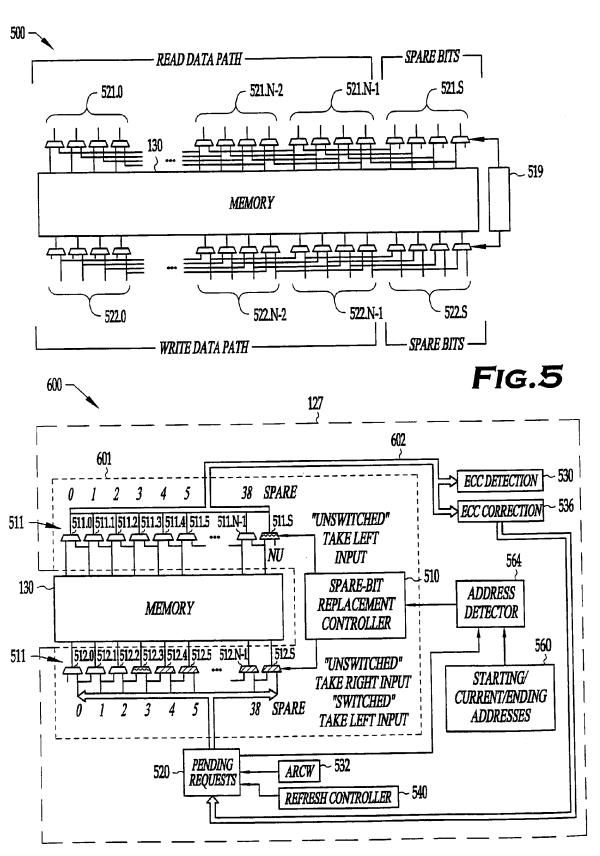

FIG. 5 is a block diagram of a multiple-bit-swapping circuit 500 of some embodiments of the invention.

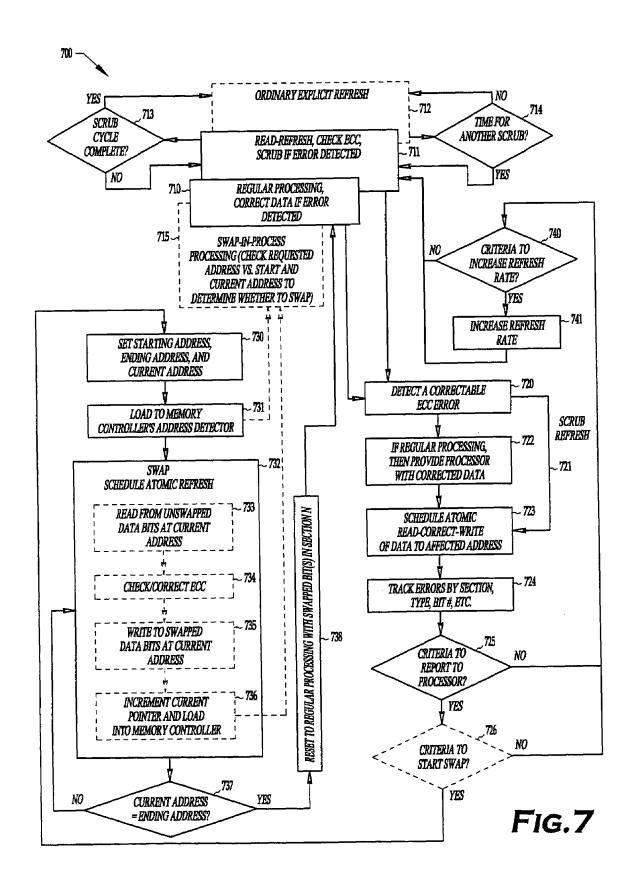

FIG. 6 is a block diagram of an address-range bit-swapping circuit 600 of some embodiments of the invention.

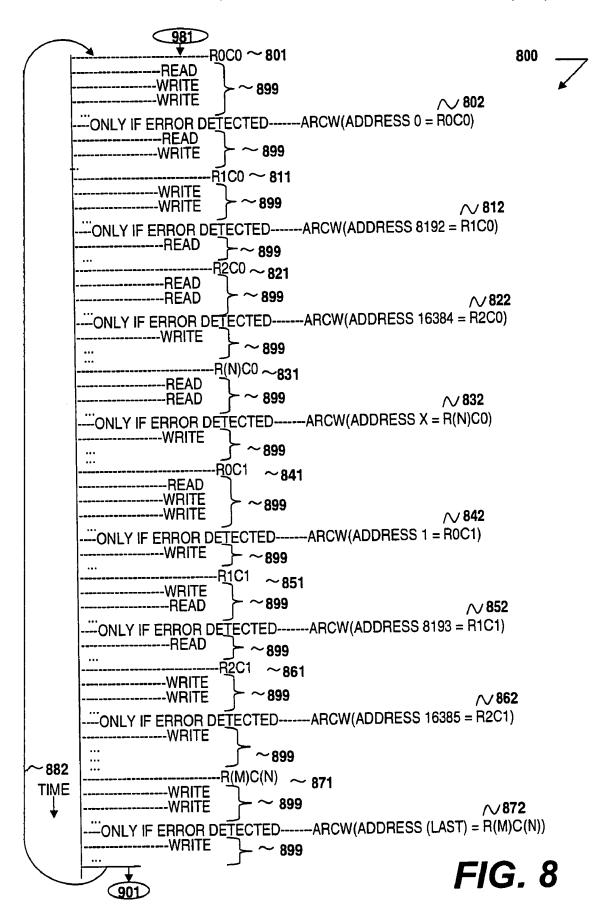

FIG. 7 is a flowchart block diagram of refresh/scrubbing/bit-swapping process 700 of some embodiments of the invention.

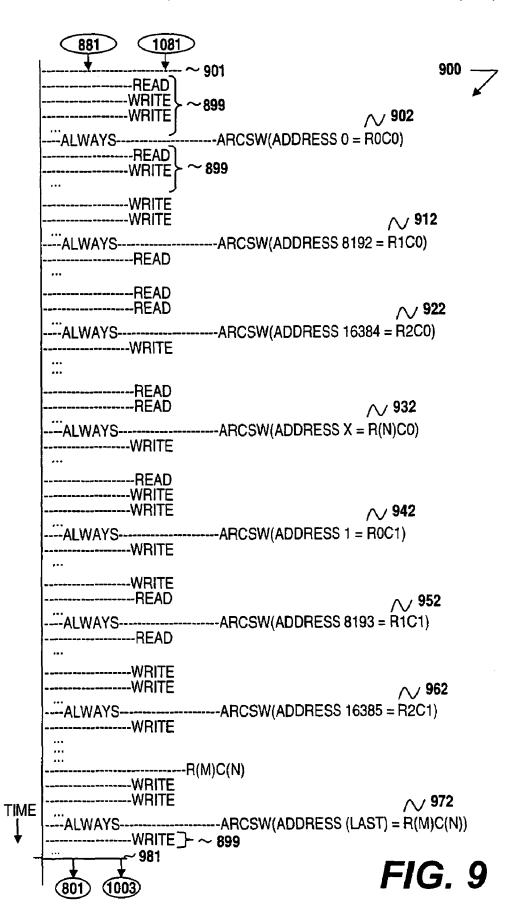

FIG. 8 is a schematic flowchart 800 used in some embodiments.

FIG.  $\bf 9$  is a schematic flowchart  $\bf 900$  used in some embodiments.

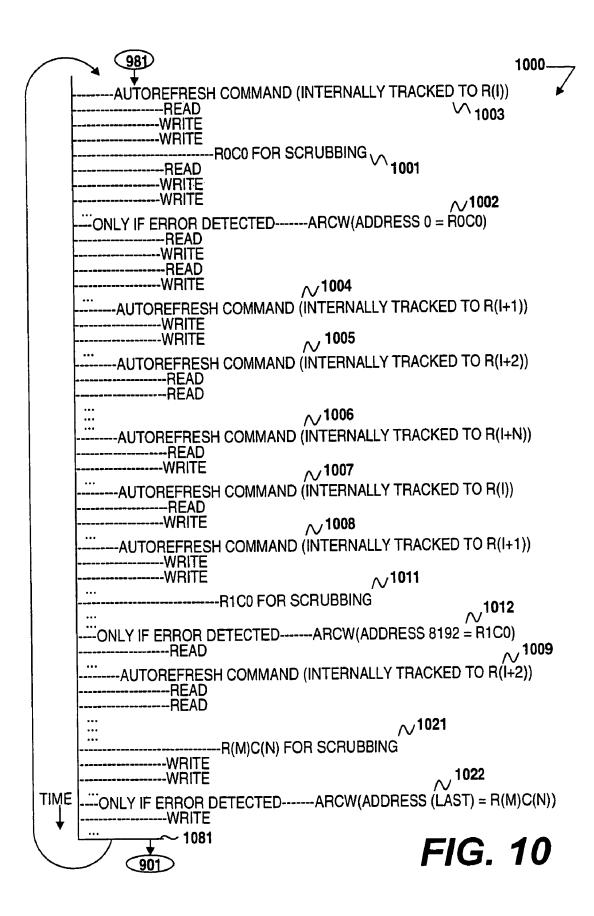

FIG. 10 is a schematic flowchart 1000 used in some embodiments.

## DESCRIPTION OF PREFERRED EMBODIMENTS

In the following detailed description of the preferred embodiments, reference is made to the accompanying drawings that form a part hereof, and in which are shown by way of illustration specific embodiments in which the invention may be practiced. It is understood that other embodiments may be utilized and structural changes may be made without departing from the scope of the present invention.

The leading digit(s) of reference numbers appearing in the Figures generally correspond to the Figure number in which that component is first introduced, such that the same reference number is used throughout to refer to an identical component which appears in multiple Figures. Signals and connections may be referred to by the same reference number or label, and the actual meaning will be clear from its use in the context of the description.

#### System Environment

FIG. 1A is a block diagram of a computer system 100 of some embodiments of the invention. Computer system 100 includes an interconnection network 99 that is connected to one or more boards 102, each board having one or more nodes 101 (for example one or two nodes 101 per board 102), each node 101 having one or more PEs (processing elements, also called processor units, or processors) 106 (for example, four processing elements 106 are used in some embodiments), each node 101 having one or more memory daughter cards (MDCs) 110 (for example, up to thirty-two MDCs 110 per node 101, in some embodiments). In some embodiments, a node controller, router, and interconnection scheme such as described in U.S. patent application Ser. No. 09/407,428 filed Sep. 29, 1999 and entitled "MULTIPRO-CESSOR NODE CONTROLLER CIRCUIT METHOD" is used with node 101. In some embodiments, each PE 106 has six connections to network 99 (e.g., a multi-dimensional network, two each in each of three directions, and which, for example, can be used to form a torus (optionally multidimensional) interconnection), while in other embodiments, other numbers of connections are made

to construct different network topologies. In typical systems, a power supply system 181 supplies power, and an input/output system 182 provides data input and output, such as to and from disk and/or tape storage devices, and/or user consoles.

FIG. 1B is in further explanation of the embodiment of computer system 100. Computer system 100 includes an interconnection network 99 that is connected to a plurality of nodes 101, each node 101 having a processor group 105 having one or more processing elements 106 (for example, 10 four processing elements are used in some embodiments), each node 101 having one or more memory daughter cards (MDCs) 110 (for example, up to thirty-two MDCs 110 per node 101, in some embodiments). In some embodiments, all of the MDCs 110 of a node are each connected to all of the 15 processors 106 of that node (e.g., in some embodiments, each of the four ports (e.g., SERDES interfaces) 121 of each MDC 110 is connected to a different one of the plurality of processors 106).

In some embodiments, each MDC 110 includes a single 20 W-chip or W-circuit 120 (i.e., a circuit 120, which, in some embodiments, is implemented on a single chip (and, in some embodiments, includes other circuitry and/or functions than described herein), but in other embodiments, can be implemented on multiple chips, or a processor, or on a memory 25 chip or using other configurations), but in other embodiments, circuit 120 is implemented using more than one chip, but is designated herein as W-chip or circuit 120) having a high-speed external card interface 112, which in turn includes a plurality of SerDes (serializer-deserializer) ports 30 121 (for example, four SerDes ports 121 per MDC 110 are used in some embodiments). A crossbar switch 123 connects each SerDes port 121 to each one of a plurality of L3 caches 124 (for example, four L3 caches 124 per MDC 110 are provided in some embodiments). In some embodiments, 35 each L3 cache 124 is tied by connection 126 to a corresponding DDR2 memory controller 127. In some embodiments, an additional "degrade capability" connection 128 is provided between each L3 cache 124 and a neighboring DDR2 memory controller 127. In some embodiments, each 40 DDR2 memory controller 127 controls five eight-bit-wide DDR2 memory-chip groups 130 (for example, each chip group 130 having one memory chip, or having two or more stacked chips). This provides each DDR2 memory controller 127 with a forty-bit-wide data path, providing 32 data bits, 45 seven ECC (error-correction code) bits, and a spare bit.

In some embodiments, the individual memory components of the memory-chip group(s) 130 conform to the emerging JEDEC Standards Committee DDR2 SDRAM Data Sheet Revision 1.0 Specification JC 42.3 (JESD79-2 50 Revision 1.0) dated Feb. 3, 2003 or subsequent versions thereof. In other embodiments, conventional, readily available DDR chips are used. In yet other embodiments, any suitable memory-chip technology (such as Rambus (tm), SDRAM, SRAM, EEPROM, Flash memory, etc.) is used for 55 memory-chip groups 130.

In some embodiments, each DDR2 memory controller 127 controls five eight-bit-wide DDR2 memory-chip groups 130 (for example, each chip group 130 having one memory rank, or having two or more ranks with possibly stacked 60 memory chips). This provides each DDR2 memory controller 127 with a forty-bit-wide data path, providing 32 data bits, seven ECC (error-correction code) bits, and a spare bit.

The W-circuit **120** also includes a control interface **122** (some embodiments use a JTAG-type boundary-scan circuit for control interface **122**; some other embodiments use a Firewire (IEEE Standard 1394) channel (or other standard or

8

custom interface channel) for the off-card interface 119 to control interface circuit 122). In some embodiments, the Firewire interface is built into W-circuit 120, while in other embodiments, the Firewire interface is built on a separate chip on MDC 110, and connects to a JTAG interface provided by control interface 122. Control interface 122 provides the mechanism to set bit patterns in configuration registers (for example, some embodiments use memorymapped registers (MMRs) 141) that hold variables that control the operation of W-circuit 120.

The present invention also provides circuitry that allows one MDC 110 to test another MDC 110, in some embodiments, or to test itself, in other embodiments. In some embodiments, this circuitry is implemented as a W-circuit test engine (WTE) 125 having a microcode sequence, described further below.

FIG. 2A is a block diagram of a memory-daughter-card testing system 200 of some embodiments of the invention. In some embodiments, MDC testing system 200 includes a test fixture 210 having two or more MDCs 110 plugged into it. Connections 230 couple each output of each SerDes port 121 to a corresponding input of a SerDes port 121 on another MDC 110, thus allowing the test to run each MDC 110 at full speed through its normal read/write interface. The test fixture 210 provides clocks 222 from clock generator 240 (e.g., high-speed differential clocks) used by the MDCs 110, and also includes a test controller 220 that programs one or the other or both WTEs 125 (e.g., through its ports 219A and 219B coupled to the respective ports 119 to control interfaces 122). In some embodiments, test controller 220 sets up one MDC 110 (for example, the lower one) as the tester card wherein its WTE 125 runs the memory tests, and sets up the other MDC 110 (for example, the upper one) as the unitunder-test (UUT) wherein it is configured in the normal read/write memory card mode (as if it were in system 100 of FIG. 1A). Thus, the lower WTE 125 sets up data patterns in its memory-chip groups 130 (at the bottom of FIG. 2A), and then controls the writing of these patterns out the SerDes port 121 of the lower MDC 110, and thus into the SerDes of the upper MDC 110, and into that MDC's caches 124 and memory-chip groups 130. These data patterns are then read back the opposite way (or, in some embodiments, the UUT itself checks read operands from the memory being tested), and compared by WTE 125 in the lower MDC 110. When each test is complete, the results are transferred back to test controller 220 for analysis and use in accepting, rejecting, or reconfiguring the WUT MDC 110.

In some embodiments, such a configuration allows a large variety of debug activities to be performed that are not available on simpler setups that run a large number of tests, but generate only a pass-fail result, such as checking a checksum value after a large number of tests were run. The ability to load microcode having newly devised tests allows intricate debug to be performed, even when the high-speed interfaces (SerDes ports 121, for example) are run at full speed

FIG. 2B is a block diagram of a memory-daughter-card testing system 201 of some embodiments of the invention. In some embodiments, MDC testing system 201 includes a test fixture 211 having a single MDC 10 plugged into it. Connections 231 couple each output of a subset of SerDes ports 121 to a corresponding input of another SerDes port 121 on the same MDC 110, and the test controller's control port 219 is connected to the MDC's port 119 of control interface 122, thus allowing the test to run the MDC 110 at full speed through its normal read/write interface.

In some embodiments, the test fixture 211 (which is similar to fixture 210 of FIG. 2A, except that loop-back connections are made in the test fixture 211 between ports 0 and 1, and ports 2 and 3 of MDC 110) provides clocks 222 (e.g., high-speed differential clocks) used by the MDCs 110, and also includes a test controller 220 that programs the single WTE 125. In other embodiments, one or both MDCs 110 generates its own clocks for its transmitter, which clocks are then received and used by the other MDC 110.

In some embodiments, test controller 220 sets up one or more SerDes ports 121 (for example, port 0 and port 2) as the tester port(s) wherein WTE 125 runs the memory tests out those ports and receives results back into those ports), and sets up the other ports 121 (for example, ports 1 and 3) as the unit-under-test (UUT) ports wherein they are configured in the normal read/write memory card mode (as if it were in system 100 of FIG. 1A). Thus, in some embodiments, the even-numbered ports set up data patterns in their respective memory-chip groups 130, and then controls the writing of these patterns out the even-numbered SerDes port 121, and thus into the odd-numbered SerDes port 121 next to them, and into those port's caches 124 and memory-chip groups 130. These data patterns are then read back the opposite way and compared by WTE 125. When each test is complete, the results are transferred back to test controller 220 for analysis and use in accepting, rejecting, or reconfiguring the UUT MDC 110. This way of testing allows the tests to cover the complete data path from the memories to the edge of the card. Further, only the single MDC 110 is required for the test.

In some embodiments, a test-control computer **288** is provided to drive test controller **220**, and to receive results for display, transmission, or storage. In some embodiments, a computer-readable storage medium **289** (such as diskette or CDROM) is used to provide the control program data that is loaded into microcode memory **310** of FIG. **2F**, described below. This control program data provides the data and control flow to allow, e.g., one MDC **110** to test another MDC **110**. In some embodiments, an external master clock oscillator **287** provides a source signal for clock generator **240**.

In other embodiments, a computer-readable storage medium **289** is provided that includes instructions stored thereon for causing a suitably programmed information-processing system to execute one or more of the methods described herein.

FIG. 2C is a block diagram of a memory-daughter-card testing system 202 of some embodiments of the invention. In some embodiments, MDC testing system 202 includes a 50 test fixture 212 (which is similar to fixture 211 of FIG. 2B, except no electrical connections are made in the test fixture 211 to ports 0, 1, 2 and 3 of MDC 110) having a single MDC 110 plugged into it. Connections (in some embodiments, these are programmably connectable by microcoding WTE 55 125) are configured on board the MDC 110, rather than in the test fixture as was the case for FIGS. 2B and 2A. In other embodiments, the connections are physically wired (e.g., by card traces, jumpers or soldered "blue wires" that are later removed or cut (for example, by a laser or other suitable 60 method) for normal operation of the card (thus making the test card temporarily not quite exactly identical to the normally operating card). These on-card connections couple each output of a subset of SerDes ports 121 to a corresponding input of another SerDes port 121 on the same MDC 110, 65 thus allowing the test to run the MDC 110 at full speed through its normal read/write interface. Although, this does

10

not allow the testing to the card edge as was the case for FIG. 2B, in other ways the operation of FIG. 2C is the same as for FIG. 2B

FIG. 2D shows a similar system 203 having local SerDes Connections, connected by gates 221 under the control of loop-back controller 223 as directed by WTE 125, in some embodiments, within the IC that allow local testing of the SerDes functions before the IC is mounted on the MDC 110 and afterward. The output of each port 121 is returned to the input of the same port within W-circuit 120. In some embodiments, no actual connections to the high-speed serial ports need to be made to the test fixture 213. In some embodiments, MDC testing system 203's test fixture 213 (which is similar to fixture 211 of FIG. 2B, except no electrical connections are made in the test fixture 211 to ports 0, 1, 2 and 3 of MDC 110) has one or more MDCs 110 plugged into it.

FIG. 2E is a block diagram of a portion of W-circuit 120 of some embodiments of the invention, showing more detail than is shown in FIG. 1A. In some embodiments, W-circuit 120 includes a control interface 122 (for example, a JTAGtype scan-register interface and associated control registers), a WTE 125, a crossbar 123 that connects each of four SerDes ports 121 (two are shown here) to each of four L3 caches 124 (two are shown here), which are in turn coupled to a corresponding memory controller 127 (two of four are shown here). WTE 125 includes a test generation component 346 and a test results component 347 that compares results obtained by selection circuitry 348 that obtains results from the SerDes-in sections 341 or the crossbar-out sections 352. Each port 121 includes a SerDes-in 341 portion that feeds a corresponding Link Control Block-in (LCB-in) circuit 342, and a multiplexer (selector) 343 that obtains data from test generator 346, and crossbar-out circuit 352 and selects one of those to feed to LCB-out circuit 344 and then to SerDesout portion 345. The crossbar-in portion 351 obtains data from each input port (i.e., from the output of its LCB-in 342) and directs that data to one of the four L3 caches 124. The crossbar-out portion 352 obtains data from one of the four 40 L3 caches 124, and directs that data to one of the four output ports 121 (i.e., to the input of its LCB-out 344 through its selector 343).

In some embodiments, the cache quadrants 124 each drive separate memory controllers 127. In turn, each memory controller drives a set of memory chips 130.

FIG. 2F is a block diagram of a test-engine processor 346 of some embodiments of the invention. Test-engine processor 346 provides test generation functions for WTE 125. Programming and data patterns 301 are sent from test controller 220 (see FIG. 1B) through control interface 122, and delivered to microcode memory 310 and test data buffer 326. Some embodiments include a pseudo-random number generator 328 that provides pseudo-random numbers as source test operands to test data buffer 326 and to the expected-result-data buffer 428 (see FIG. 4) instead of loading tests from the control interface 122. Microcode memory 310 provides instructions 316 in a manner programmed into the control words stored there and sequenced by sequencer 312 that includes a loop counter/controller 314, and that generates each next address 313 (e.g., sequential execution, looping, branching, etc.). Instructions 316 also include data, command, and selection fields to test data buffer 326, address register 324 and its address adder 322, command register 320, and build-test-packet controller 330. Build-test-packet controller 330 in turn receives commands from command register 320, addresses from address register 324, and data (i.e., patterns to be written, read, and com-

pared) from test data buffer 326. Build-test-packet controller 330 sends test packets 331 to the crossbar-in 351, which forwards them the L3 cache 124 or the memory controllers 127 and then the memory 130 on the tester MDC 110, and sends TIDs (Transaction IDentifiers) to the result-data 5 indexes buffer 422 (see FIG. 4). The test controller 125 can also send test data to the 343 multiplexers and thence to the SerDes ports 121.

FIG. 2G is a block diagram of a test-engine test-result checker (TETRC) 347 of some embodiments of the invention. TETRC 347 includes an expected-result-data buffer 428 that receives fill data 401 from JTAG control interface 122 (see FIG. 1B), pseudo-random data 416 from pseudorandom number generator 328, and result data indexes 418 an address that is used to read expected result data items 15 from result-data indexes buffer 422, and sends operands for comparison operations performed by compare circuit 424. In other words, the TID (transaction ID) is used as an address into the result data indexes buffer 422, and obtains a pointer 418 that points to an entry having the comparison data in 20 expected result data buffer 428. Result-data indexes buffer 422 receives TIDs from build-test-packet controller 330, data results field data 412 from microcode memory 310, and returned TID data 430 test results selected through multiplexer 348 (see FIG. 2E) from the UUT MDC 110; result- 25 data indexes buffer 422 provides the pointer 418 corresponding to the input TID as an operand (index to retrieve data pattern) to expected-result-data buffer 428. Thus, each TID 410 corresponds to a particular data pattern, and the returned results data includes a TID 423 and data pattern 421, which 30 are correlated by the circuitry such that compare circuit receives the expected data 420 and the returned result data **421** in a time sequence that allows the proper data to be compared, and if the data does not compare properly, and error indication 434 is provided to control interface 122. In 35 some embodiments, a result-data memory 426 provides storage for a series of results that are delivered as data 436 to JTAG control interface 122.

Thus, the memory daughter card (MDC) 110 for computer system 100 is very different from conventional memory 40 cards designed and used previously in the computer industry. MDC 110 does not provide direct access to the memory parts on the card from the card's connector, but instead it receives commands and functional requests through four high-speed ports 121 that can not easily be connected to, or functionally 45 tested by, general-purpose testers or conventional memory testers. This means that test capability of the card must be designed into the card as part of the design process and, in some embodiments, needs to interact with and accept test requirements of the vendor or vendors that will manufacture 50 the card. This invention describes the basic test requirements and capabilities in support of all aspects of making and using a MDC 110: in card manufacturing and test, in initial system debug and checkout, in field test and support, in card repair,

The test capability described here is typically not intended to replace a multimillion-dollar test system, but to enable verification of correct operation of all components on the card and to support maintenance and debugging functions when needed.

Error Correction and Reliability Enhancement

FIG. 3 is a block diagram of a computer system (having a single node 101) of some embodiments of the invention, showing some details of a memory controller 127. In some 65 embodiments, each of one or more each memory daughter cards 110 includes a W-chip or circuit 120 that includes one

**12**

or more memory controllers 127, each of which drives a plurality of memory parts (or chips) 130.

For example, in some embodiments, each memory controller 127 drives one or more sets 131 of chips 130, each set 131 having five DDR2 DRAM chips 130, each chip 130 having an eight-bit-wide data interface, for a total of forty (40) data bits going to and from each memory controller 127. Depending on the context, "set 131" is also referred to as "memory portion 131" that is connected to one memory controller 127 (for embodiments having a plurality of memory controllers 127 each having a memory portion 131), or as "memory 131" that is connected memory controller 127 (for embodiments having one memory controller 127 having a memory 131, wherein the memory portion is all of memory). In these embodiments, this provides 32 program data bits, 7 ECC data bits and one spare data bit. Other embodiments use other widths of data interfaces to the individual memory chips (e.g., 1-bit, 4-bit, 16-bit, 32-bit, or other width interfaces), and other numbers of program data bits (e.g., 64 or 128), ECC data bits (e.g., 8 or more), and/or spare data bits (e.g., 2 or more). In some embodiments, an ECC coding scheme is chosen to correct all single-bit errors and not only detect all two-bit errors, but also to detect many or all package-wide errors. (See, for example, U.S. Pat. No. 5,745,508 "ERROR-DETECTION CODE" by Thomas Prohofsky, which is incorporated herein by reference).

In some embodiments, a queue, buffer, or pipeline of pending requests 520 is provided that accepts read and write requests at high burst rates from the processor(s) and send requests to the memory parts 130 at a rate that can be handled by those parts, and in some embodiments, this pipeline 520 also generates the ECC check bits for the data being written. In some embodiments, an external refresh controller 540 is provided in the W-circuit 120, which inserts read-refresh requests into request pipeline 520, which also primarily holds the read and write requests from the processors 106. In some embodiments, external refresh controller 540 includes a refresh row counter 548 and a refresh column counter 546. The row counter 548 cycles through all the rows of the memory parts frequently enough to meet the refresh-frequency requirements of the memory parts, which frequency is sufficient to refresh the memory parts across all rows regardless of the value that is provided for the column address during the refresh-read request.

As used herein, a read-refresh mode of operation is one in which normal read-operation requests (called "read-refresh requests") are inserted into a stream of memory requests (for example, in some embodiments, these come from processors 106 and are held in pipeline 520), the read-refresh requests eventually specifying each and every row address in memory within the required refresh interval of the memory parts. In some embodiments, scrub operations are executed on each successive cycle of rows, by specifying and reading data from a different column address, and performing ECC checking. If a correctable data error is detected when reading, then the corrected data is written back to the affected location (a scrub operation). The read-refresh mode of operation is controlled by refresh controller 540.

In contrast, an explicit-refresh mode of operation is one in which the internal refresh function within the memory parts is invoked, typically by sending a refresh command rather than a normal read command. In some embodiments, the memory parts then go into a somewhat extended refresh mode that refreshes one or more internal banks and/or rows based on internal counters not visible to the external

memory controller. In some embodiments, the explicitrefresh mode of operation is also controlled by refresh controller **540**.

In some embodiments, a priority controller 522 is provided, wherein requests from processors 106 are typically given higher priority (and, in some embodiments, the processors 106 can specify a priority for each of their requests), and requests from the refresh controller 540 are typically given lower priority. However, if a lower-priority refresh request has been held off for too long a time, timer 542 and refresh-priority adjuster 544 specify to priority controller 522 to increase the priority of the old refresh requests, in order that the refresh-frequency requirements of the parts are met, and data are not lost.

In some embodiments, for read requests and read-refresh requests, the DRAM chips 130 are first sent (from memory controller 127) a row address using a subset of the address bits, which causes one entire row of data bits (e.g., 8,192 bits, in some embodiments) to be read into internal row latches. The DRAM chips 130 are then sent a column address (e.g., eight bits) that selects one set of, e.g., 32 bits selected from the 8,192 row bits. The selected 32 bits are then multiplexed to four successive sets of eight bits that are sent in a burst (i.e., four successive 8-bit bytes are sent from each of five chips 130, thus providing the memory controller four successive data words from each set of chips 130, each word having thirty-two program-data bits, seven ECC-data bits and one spare data bit, for example).

In some embodiments, ECC, refresh and scrubbing, and/ or bit swapping, as described for the present invention, are implemented inside each memory chip 130. For example, in some embodiments, each row inside a memory chip further includes the ECC bits (e.g., 2048 ECC bits for 8192 data bits using a 32+7-bit data word, or 1024 ECC bits for 8192 data bits using a 64+8-bit data word) and/or spare bits. When a column address is sent, both data and ECC bits, and optionally spare bits (e.g., for a total of 40 bits, in some embodiments), are selected from the desired row, and are multiplexed to, e.g., five successive sets of eight bits, that are sent in a burst (e.g., five successive 8-bit bytes are sent from one chip 130, thus providing the memory controller four successive program-data bytes and one extra byte having seven ECC-data bits and one spare data bit, for example, or four successive 10-bit pieces could be output in other embodiments). Other embodiments could implement, e.g., 64 data bits, 8 ECC bits, and N spare bits (the external interface could burst, for example, nine 8-bit portions, eight 9-bit portions, or four 18-bit portions). Such embodiments (having any arbitrary number of data bits and a sufficient number of ECC bits for each address) allow some or all of the ECC checking and correction of block 530, the ARCW unit 532, the bit swapping of units 560 and 510, and/or the scrubbing and refresh functions of block 540 to be implemented inside each one of memory chips 130.

In modern memory technology, other data widths are available (4-bit wide data path, 8 (-bit wide data path (as described herein), 16-bit wide data path, and 32-bit wide data path). Before another reference is made to the same bank, the content of the associated row buffer is written to the same row location from which it was read. This accomplishes the refresh function and also saves any write data that was changed (written) in the row buffer.

This, and different page sizes (number of bits in a single row of a single bank), make the mapping of which memory bits are row and column selects more complex. In addition this affects the column multiplexer and also affects the 14

distributed-refresh function (and therefore the other functions) in a computer's design.

The ECC circuitry in ECC-checking pipeline 530 is used to detect single- and double-bit (and certain multi-bit) errors and correct single-bit errors in each of the successive four words. In some embodiments, the four words are corrected (as needed) on the fly through pipeline 530, and four correct words are sent to the processors 106, if the read request was from the processors (read data 380 from read-refresh requests are discarded). In other embodiments, the four words are sent raw towards the processors in a pipeline, and if an error is detected, then a subsequent command tells the processor to hold or abort processing on the raw words and wait for corrected data to be sent.

In some embodiments, if an error is detected by ECC checking circuit 530 in any of the four words read, information identifying the location having the error, and other information regarding the error (such as the type of error, which bit had the error, etc.) is logged in a error-log buffer 534 on the W-circuit 120. In some embodiments, by the time the error is detected, one of a plurality of processors could have sent write data to the affected location, thus changing the data at the location. Thus, in such embodiments, it is undesirable for the memory controller to write the corrected version of the originally read data directly back to the memory-chip location, since it could overwrite newer data that was written by other sources in the meantime.

In some embodiments, at least a portion of the refresh function is also performed by refresh controller **540** sched30 uling normal read-refresh operations into queue **520**, and also providing a scrubbing function (performing a correction and write back if an error was found in the read-refresh data). This also could cause problems if the memory controller **127** were to write the corrected version of the read-refresh data directly back to the memory-chip location, since it could overwrite newer data that was written by the processor(s) in the mean time.

Thus, one aspect of the invention is, if a correctable error is detected, for the atomic read-correct-write (ARCW) con-40 troller 532 of W-circuit 120 to insert, into the queue 520 of pending memory operations, a command that performs an atomic read-correct-write operation, wherein the affected section of memory is idled (the processors and other users of the memory are temporally locked out of performing operations there, and pending operations from the queue 520 for the requested memory bank are not allowed to issue until the ARCW completes), then the data from the affected location is again read, ECC circuit 530 is used to detect and possibly correct error(s) (since one or more further errors may have occurred since the first correctable error was detected, resulting in an uncorrectable double-bit error, or a processor could have written new data to the location, thus possibly eliminating the error, especially for bits having "soft" errors that go away when good data is written, in contrast to "hard" 55 errors that remain stuck), and if corrected data is obtainable, it is written back to the affected location, and a log entry is made into error-log buffer 534.

In some embodiments, in each memory controller 127, the queue 520 is implemented as a buffer of pending memory requests connected to one or more inputs of an arbitration circuit that selects and issues which memory request is sent next to the section of memory 131 connected to that controller 127. The output of the arbitration circuit is connected to the section of memory 131, and includes the memory request that is issued to that portion of memory 131 for that memory controller 127. In some embodiments, the requests for read-refresh, explicit refresh (IN SOME EMBODI-

MENTS, SIMPLY IMPLEMENTED BY A TIMER), and/or atomic read-correct-(optionally swapping bits)-and-write (ARCW) operations are placed in registers that also input to the arbitration circuit, such that the arbitration circuit can choose between a processor-sourced memory-request opera- 5 tion and a pending refresh (or ARCW) operation. Since the pending refresh requests are not in arbitrary locations in the buffer, but are instead in specific registers, the refresh controller 540 can access and increase their priority if too much time has passed, thus forcing the arbitration circuit to 10 service those requests within the refresh interval required by the memory parts. Early in a given refresh interval, the arbitration circuit would select processor-source memory requests, and only if none of those were pending would the refresh request be issued. Later in the refresh interval, the 15 priority of the refresh request is increased, and the arbitration circuit would immediately choose to issue the refresh request. In some embodiments, the priority of the ARCW operation to correct a single-bit ECC-correctable error could also be set at low priority initially (the arbitration circuit 20 giving priority to processor-sourced memory requests at that time), and then later be set to a higher priority, in order that the error is corrected before a further bit error occurred at that location to making the error uncorrectable.

In some embodiments, the arbitration circuit of queue 520 25 will prevent a conflicting access from being issued, i.e., during the operation of an ARCW or other atomic operation to a portion of memory (e.g., one bank), other accesses to that portion of memory will be inhibited, but accesses to other portions of memory will be issued and performed. In 30 some embodiments, each set 131 of memory chips 130 has a plurality of banks (e.g., in some embodiments, eight banks for each controller 127), so when an ARCW or atomic swap-bits operation is being performed to a location in one of the banks, other accesses to that bank are inhibited, but 35 accesses to the other banks (e.g., the other seven banks) continue to be issued. In some embodiments, explicit refresh operations affect all banks for one memory-chip set 131, so explicit refreshes stop accesses to all banks, in contrast to read-refresh operations that affect only a single banks at a 40 time and can be interleaved and arbitrated more efficiently, thus providing enhanced performance.

If the error was not correctable (i.e., from multiple-bit errors), a log entry is made indicating that (more severe) error. In some embodiments, the logged errors are accumulated and (possibly later) reported to the processor. In some embodiments, one or more further ARCW operations are performed to determine whether the error is a hard error (one that was not corrected by simply writing correct data to the location, as indicated by the same error being again 50 detected) or a soft error (one that is corrected by simply writing correct data to the location, wherein no error is detected on subsequent reads), and the result of that determination is logged and possibly reported.

Once these operations are completed, the hold is removed 55 from the affected section or bank, and operations from the processor(s) are allowed to resume (e.g., by such requests again being allowed from queue 520). In some embodiments, only requests for the memory bank whose data is being referenced are held (i.e., kept in the buffer and 60 prevented from being sent to the memory parts), allowing normal memory references to occur to the other memory banks. In some embodiments, this comes at a cost of a more complex queuing and buffering implementation.

As used herein, an "atomic" (meaning "indivisible") 65 read-correct-write (ARCW) operation is one in which, for at least the affected address, no other memory-access operation

16

is allowed after the read portion and before the write portion. Some embodiments lock only the one location addressed by the ARCW but allow other read or write operations to access any other locations in memory since the ARCW operation need be only relatively atomic (atomic as to the location affected). Other embodiments lock the one section or bank of memory that includes the affected address and allow accesses to other sections or banks, and yet other embodiments lock larger portions or the entire memory for the duration of the ARCW operation. Thus, in some embodiments, an ARCW operation causes the queue 520 for only one memory controller 127 to be emptied (for example, in some embodiments, the pending operations are allowed to complete, but no other operations are accepted until the write portion of the operation commits to complete; e.g., the write operation with the corrected data could be in the queue with the highest priority, and then the queue could accept requests having a priority that would not pre-empt the atomic write portion, or the other operations could be made to wait until the operation finished.) This makes the ARCW "atomic" by locking out any requests for all addresses in that section or bank of memory connected to that particular memory controller 127. In other embodiments, the atomic ARCW locks out requests for only a subset of addresses in the affected section of memory, for example, only the single address that is to be touched by the ARCW operation, or only a row or other subset of addresses. Thus, to be "atomic," no other operations are allowed at least to the affected address, and in some embodiments, a larger number of addresses are affected in order to simplify the circuitry and control, for example, the atomic lockout could affect the entire section of memory chips attached to one memory controller 127, or to all the memory sections attached to one MDC 110.

In some embodiments, the ARCW function is relatively independent of whether a normal processor read request caused the memory reference that resulted in the detected error indication, or whether a read-refresh request caused the memory reference that resulted in the detected error indication, in that the same ARCW operation is performed and inserted into the stream of requests to a memory controller 127. Notice though that during a bit-swapping operation, the read operation is performed using the normal bit mapping, and the write operation is performed using the bit-swapped mapping.

In some embodiments, the bit-swapping operation is performed by logic that uses or shares the refresh circuitry. In some embodiments, when a bit-swapping operation is being done, no initial read-refresh operation is performed and only the ARCW operation portion is done at each successive address in the portion of memory that will be affected by the bit-swapped mapping, since the ARCW is refreshing the addresses it uses when row-sequencing is done fast enough to meet the refresh requirements of the memory parts, and since an ARCW operation will be scheduled regardless of whether an error is detected or not, then no regular read need be done. Since the ARCW operations are performed on the timetable required by the refresh circuitry, no separate read-refresh operation need be scheduled for the affected portion of memory though the timing requirements of Refresh will determine at least a portion of the address sequence.

While, in some embodiments such as those shown, the request queue 520, ECC checking pipeline 530, and refresh controller 540 are shown within memory controller 127, in other embodiments, they can be implemented externally within W-chip or circuit 120.

In some embodiments, the memory chips 130 also include an internal refresh controller (IRC) 550, each of which has its own row counter, since AutoRefresh is a standard feature of most current DRAMs. When memory chips 130 receives an explicit refresh command (which is separate and not 5 related to the read-refresh requests discussed above), the chips 130 go into an internal refresh mode and refreshes one or more rows of memory bits in one or more of its banks. In some embodiments, this takes a relatively long time, during which regular read and write requests are locked out, resulting, e.g., in up to 2.2% overhead for explicit refresh. If the read-refresh request mode of operation takes less time than the explicit-refresh mode, then read-refresh mode can be used, and explicit refresh commands would not be sent and the internal refresh controller in the memory chips would not 15 be used.

If, however, the read-refresh request mode of operation takes more time (i.e., costs a higher percentage overhead) than the explicit-refresh mode, then the read-refresh mode is used at a lower frequency (generally a much lower frequency) in order to scrub memory of soft single-bit errors, and explicit-refresh commands are sent and the memory chip's internal refresh controller is used. For example, if the read-refresh mode takes 3.6% overhead and the explicit-refresh mode take only 2.2% overhead, there is a performance gain by using the explicit-refresh mode at least part of the time, but at the cost of not as often performing the scrub operation that is included in the read-refresh mode of operation.

In some embodiments, a bit-swapping circuit 600 is 30 provided, whereby if a bit in the memory data-bus interface 129 or in chips 130 is detected as faulty, failing, or questionable, that bit can be swapped out. In some embodiments, one of the processors 106 sends a command through control interface 122 to cause the swapping to occur, and specifies 35 a range of addresses within which the bit will be swapped. In some embodiments, the starting address to swap is zero (such that starting address 561 can be assumed to be zero, simplifying the address compares that need to be performed, and increasing the possible speed) within a given section or 40 bank of memory, and successive addresses (i.e., 0, 1, 2, ...) are swapped until all addresses within the entire bank or section of memory are handled. Having a zero starting address and a power-of-two size simplifies range checking. In other embodiments, a non-zero starting address can be 45 specified, and/or a non-power-of-two size can be specified, in order to be able to handle differently swapped bits within a given memory space. Then, when a normal read or write access request is received, an address 565 from pipeline 520 is compared by address detector 564, and if it is found to be 50 between a starting address 561 and a current address 562, then address detector 564 commands bit-swapping controller (also called the spare-bit replacement controller) 510 to shift all bits on one side of the failing bit, in order to use the spare bit and ignore the failing bit, as described below.

Some embodiments further include a background-replacement operation (in some embodiments, as part of the read-refresh mode of operation) that reads data from each successive location in an identified section of memory under the original bit allocation scheme, corrects the data if need 60 be, and writes the data (as corrected) back to its location using the bit-shifted scheme that eliminates a failed or questionable bit and instead uses the spare bit. The ending address 563 is used by the system to specify the ending address for this series of individual swap operations, as 65 described in FIG. 7 and FIG. 8. During this replacement process, the processor can continue sending memory

18

requests to that affected section of memory, and the memory controller will map the bits to and from memory using the original bit mapping for the portion that has not been reallocated, and using the spare-bit-replacement bit mapping for the section of memory that has been reallocated with the spare bit.

FIG. 4A is a block diagram of a bit-swapping circuit 400 used by memory controller 127, used in conjunction with the address-range comparison circuitry (e.g., spare-bit replacement controller 510) in some embodiments of the invention, shown in its non-activated state. Bit-swapping circuit 400 includes a plurality of 2-bit to 1-bit read-data multiplexers 511 (i.e., 511.0, 511.1, 511.2, 511.3, 511.4, 511.5, and so on, through 511.N-1, and optional 511.S (which, in some embodiments, is included to make all the delays equal and to allow test reads from and writes to the spare bit)), which, in their "unswitched state" as shown have an output equal to their left-hand input, and in their "switched state" have an output equal to their right-hand input. Another plurality of 2-bit to 1-bit write-data multiplexers 512 are provided (i.e., 512.0, 512.1, 512.2, 512.3, 512.4, 512.5, through 512.N-1, and 512.S for the spare bit), which, in their "unswitched state" have an output equal to their right-hand input, and in their "switched state" have an output equal to their left-hand input. In the non-activated state shown in FIG. 4A, all multiplexers 511 and 512 are in their unswitched state 524, and will write the 39 data bits (numbered 0 through 38) to their normal bit positions, and will read the 39 data bits (numbered 0 through 38) from their normal bit positions. In some embodiments, the spare-bit position is written and read, along with the other memory bits, to better support memory testing, and to even the timing path lengths. In other embodiments, multiplexer 511.S and multiplexer 512.S are in "don't care" states (typically set to the unswitched state), and the spare bit is not used. Suppose, however, that bit 3 of memory is faulty (e.g., either stuck zero or one, or is often, repeatedly, or even occasionally giving soft or hard singlebit errors). In such a situation, one wants not to use bit 3, but instead to use the spare bit for reads and writes. (One understands that any of the other data bits can be replaced by the spare. Bit 3, used here, is only an example.)

FIG. 4B is a block diagram of an activated bit-swapping circuit 401 of some embodiments of the invention (i.e., the circuit of FIG. 4A, bit showing a configuration that is activated to swap bits). Rather than directly switching the spare bit and any arbitrary failed bit, the bits to one side of the failed bit are shifted one position, so that the bad bit is not used and the good spare bit is used. For example, if bit 3 failed, then on write operations source bits 0-2 are written to their normal positions by the multiplexers 512.0, 512.1, and 512.2 in their unswitched state 524, and source bit 3 and the bits to the right of bit 3 are shifted right one position by the multiplexers 512.3 through 512.N and 512.S in their switched state 525 (i.e., bit 3 gets written to memory bit-4 55 position, and source-bit 38 gets written to the memory spare-bit position). On read operations destination bits 0-2 are read from their normal memory positions by the multiplexers 511.0, 511.1, and 511.2 in their unswitched state 524 and destination bit 3 and the bits to the right of bit 3 are read and then shifted left one position by the multiplexers 511.3 through 511.N in their switched state 525 (i.e., bit 3 gets read from memory bit-4 position, and destination bit 38 gets read from the memory spare-bit position). While, in some embodiments, read multiplexer 511.S is omitted, since it is generally not switched, it is normally present so that path delays are equal and also to support of memory test functionality. Spare-bit replacement controller 510 can be

switched from activated or deactivated, or from one active state to another, between each memory access (or each access burst of four words for some DRAM architectures), thus allowing a portion of the memory to be bit-swapped, and the remainder to be unswapped.

In some embodiments, the data from each location are moved from the unswapped bit configuration to the swapped bit configuration one at a time (for example, using an atomic read-correct-write operation that forms the core of the read-refresh mode of operation), while moving the range 10 pointers as the operation proceeds, as described below.

FIG. 5 is a block diagram of a multiple-bit-swapping circuit 500 of some embodiments of the invention. Multiplebit-swapping circuit 500 includes a plurality of groups of 2-bit to 1-bit read-data multiplexers 521 (i.e., 521.0, and so 15 on, through 521.N-2, 521.N-1, and spare-bit group 521.S (which, in some embodiments, is included to make all the delays equal and to allow test reads from and writes to the spare bit)), which, in their "unswitched state" have an output equal to their left-hand input, and in their "switched state" 20 have an output equal to their right-hand input. Another plurality of groups of 2-bit to 1-bit write-data multiplexers 522 are provided (i.e., 522.0, and so on through 522.N-2, 522.N-1, and 522.S for the group of spare bits), which, in their "unswitched state" have an output equal to their 25 right-hand input, and in their "switched state" have an output equal to their left-hand input. In the non-activated state shown in FIG. 5, all multiplexer groups 521 and 522 are in their unswitched state 524 (see key of FIG. 4A), and will write the N groups of data bits (numbered 0 through N-1) 30 to their normal bit positions, and will read the N groups data bits (numbered 0 through N-1) from their normal bit positions. In the embodiment shown, there are four spare bit positions provided, and if bits are swapped, the operation is done in groups of four bits. In other embodiments, other 35 numbers of spare bits are provided. In some embodiments, the spare-bit positions are written and read, along with the other memory bits, to better support memory testing. In other embodiments, multiplexer 521.S and multiplexer 522.S are in "don't care" states (typically set to the 40 unswitched state), and the spare bits are not used. Controller 519, like the corresponding controller 510 in FIG. 4A and FIG. 6, swaps the bits for addresses within a specified range, and does not swap the bits for addresses outside that range. In some embodiments, the blocks marked 400 and 510 in 45 FIG. 3 and FIG. 6 is replaced by blocks 500 and 519 of FIG.

FIG. 6 is a block diagram of a bit-swapping and addressdetection circuit 600 including the address-detection circuitry 564 from FIG. 3, connected to a bit-steering circuit 50 601, as used in some embodiments. Circuit 601 can be implemented as a single-bit swapping circuit 400/401 of FIG. 4A and FIG. 4B, or as a multiple-bit swapping circuit 500 of FIG. 5. The address-detection circuitry 564 of block 127 is described above for FIG. 3. An ARCW operation to 55 swap one or more bits reads through the "unswitched" selectors 511 to obtain data 602 that is checked by ECC detection circuit 530 and corrected, if necessary, by correction circuit 536. The corrected data is then queued in buffer 520 and written back using the swapped configuration 60 defined by selectors 512 and the spare bit of memory 131. In some embodiments, the address of the location to be swapped is just on the outside edge of the address range defined by registers 560 (the address for which swapping takes place) when the read operation takes place. The 65 address range of registers 560 is then changed, so that the same address when used for writing the corrected data is just

20

on the inside edge the address range defined by registers 560, and detected by circuit 564.

FIG. 7 is a flowchart block diagram of refresh/scrubbing/ bit-swapping process 700 of some embodiments of the invention. Regular processing of read and write operations from processors 106 to MDCs 110 takes place at block 710, overlapped or multiplexed in time with read-refresh operations 711 and/or ordinary explicit-refresh operations 712. As discussed above, in some embodiments, if the read-refresh processing 711 takes less time or overhead, it is exclusively used for the refresh function; however, if it take less time or overhead to do the ordinary explicit-refresh function, using either a row address only from counter 548, or using a timer-controlled command that triggers an internal-refresh operation inside the memory chips 130 using internalrefresh controller 550 (see FIG. 3), then the refresh function is used for scrubbing and spare-bit insertion and will toggle between blocks 711 and 712. That is, explicit refresh block 712 will be used to save time (only if it is faster).

In some embodiments a mode bit is set at the time a system is brought into operation that controls this refreshmode choice. When explicit refresh mode block 712 is used, some embodiments include a test at block 714 to determine whether it is time for another scrub operation, and if so perform a read and check ECC (i.e., block 714), and a scrub (ARCW) if an error is detected. At decision block 713, when a sufficient amount of memory is checked and scrubbed (e.g., in some embodiments, one location at a time is scrubbed), decision block 713 will return to the explicit refresh mode 712. That is, in some embodiments, when explicit refresh mode 712 is used, an additional scrubbing read will be occasionally performed, but is not relied on for refreshing since the explicit refresh is providing that function. In some embodiments, if the read-refresh mode 711 is faster, then the dotted-line blocks 712, 713, and 714 are not

In some embodiments, the refresh function of the present invention is managed as follows: memory controller 127 provides one or both of two memory-refresh control functions: using block 712, the memory parts 130 themselves can internally perform the refresh function, wherein, in some embodiments, each memory part 130 includes an internal address counter indicating where the next refresh is to occur (the refresh operation takes place generally after a specific command is sent from the local memory controller 127) or, alternatively, using block 711, the memory controller 127 sends "normal" memory references (i.e., read commands) to the attached memory parts 130 using a specific address ordering and request rate in order that all memory bits are referenced within the required refresh interval.